Gene Frantz

Posted on April, 29, 2021

Categories

Recent Posts

- Embedded Insights #1 — How SiP Is Shaping the Future of Embedded Design June 9, 2025

- Why SiP is the Future of Embedded Systems: Insights from Octavo Systems June 3, 2025

- Revolutionizing Electronics: How Octavo Systems Simplifies Design with SiP Technology April 22, 2025

- Top 5 Tips for Getting the Most Out of Embedded World February 24, 2025

- Stargate: Unlocking AI’s Full Potential with Real-Time Contextual Data February 17, 2025

The Time Value of Design

Introduction

As processor based products become more pervasive in the industry, it seems that the time required to get a new product to market is lengthening. A major time period of getting the product to market is during the product development stage. Over my career I have seen the product development process taking from 12 months to 2 or more years. Our direction at Octavo has been to help you reduce your development time to production ramp by using system in package (SiP) technology.

The Tasks

I consider the development stage to begin with the “aha” moment of “there is a market for this new product concept” and to end when the product is ready for production ramp. If I break it down into its components:

- Design

- Layout

- Build

- Debug and qualify

Next, let me talk a bit about each aspect of the development stage.

Design

I break up the design into three aspects: 1) hardware, 2) software and 3) systems.

Hardware design

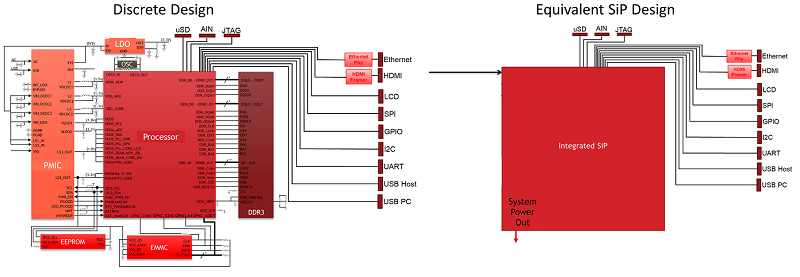

An Octavo SiP, such as the OSD335x or OSD32MP1, can make a significant impact on time to production due to the reduced complexity of the hardware as the integration of the microprocessor, power management and memory has already been designed and is properly functioning. Which leaves your hardware design task to incorporating the additional components into the product which will give your product its value. As our SiPs contain the three major processor system components along with all of the passives necessary to make them function properly, the time line is shortened not only by reducing the design activity but also the debug activity to assure that the processing system functions correctly.

Software design

The software design is simplified and shortened as the processing system is already designed and ready to be used to write, run and debug the application software on the hardware in parallel with the hardware design. This also means that early marketing samples can be made available to enable the marketing roll out to happen in parallel with the development activity. But, I’ll leave the marketing advantages of using a SiP to a later discussion.

System design

The system design needs detailed hardware and software information in order to properly do the design of the product. The ability to treat the microprocessor, memory and power management together as one component not only reduces the complexity of the PCB design but also reduces its size. It also reduces the design time of the system PCB along with the mechanical and industrial design aspects of the product.

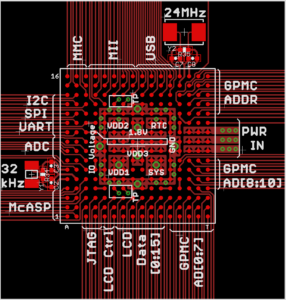

Layout

I separate the layout of the PCB from the design aspect as once the hardware is captured in a schematic, bill of material (BoM) and net list, the overall cycle collapses to 1) layout, 2) prototype build, 3) debug and 4) return to layout. Obviously, if all is done without bugs, step four become qualification rather than debug. Much of the layout complexity of your system design had been resolved within the Octavo SiP. We have also optimized the ball map so that all of the signals can escape from under the SiP in one layer of the PCB. In real terms this means that your PCB layout can easily be reduced from six or more layers to four layers. Further it is possible to finish the layout with no components needing to be placed on the back side of the PCB. That is all of the components can fit on the top surface.

I separate the layout of the PCB from the design aspect as once the hardware is captured in a schematic, bill of material (BoM) and net list, the overall cycle collapses to 1) layout, 2) prototype build, 3) debug and 4) return to layout. Obviously, if all is done without bugs, step four become qualification rather than debug. Much of the layout complexity of your system design had been resolved within the Octavo SiP. We have also optimized the ball map so that all of the signals can escape from under the SiP in one layer of the PCB. In real terms this means that your PCB layout can easily be reduced from six or more layers to four layers. Further it is possible to finish the layout with no components needing to be placed on the back side of the PCB. That is all of the components can fit on the top surface.

Prototype Build

The impact of build time for each revision of your prototypes will be minimal as once the PCB is available, the time necessary to build prototypes will be the same. The time impact will be noticed in the additional revisions of the PCB that will be need before your product can be debugged (i.e, characterized) and qualified.

Debug and qualification

The debug of the system and its qualification are for the most part an unknown aspect of the development process. By using an Octavo SiP, one of the major unknown aspects becomes known. In fact, it is reasonable to assume that the SiP processor will be used to debug and qualify the rest of the system design. And of course with a bit of additional design activity, the SiP processor can be used to perform the final test once the product is in production.

The Advantage

I have spoken with many of our customers as well as our engineering team that supports them. One of the things I like to know is how using our products affected their design. One of the biggest benefits they mention is the time that using a SiP has saved them.

Here is a summary of their estimates for the time savings for each of the tasks when using our SiP vs a Discrete solution:

| Activity | Time Saved (Months) | Cost Saved | Comments |

|---|---|---|---|

| Design | 1 | $20,000 | $20K/Staff Month |

| Layout | 2 to 5 | $40,000 to $100,000 | $20K/Staff Month |

| Build | 1.5 | $35,000 | Plus Delta Materials |

| Debug | 2 to 5 | $40,000 to $100,000 | $20K/Staff Month |

| Total Savings | 6 to 12 Months | $155,000 to $255,000 |

A point of interest is that designing with one of our SiPs seems to reduce the number of redesign cycles by one or two cycles. For completeness, I have assumed the total cost of a Staff Month (SM) is $20K and only one staff was assigned to the project. It is easy to include your cost into the equation and determine the cost savings.

Here is one final thought: The missed revenue. By not using one of our SiPs the reduced cash flow resulting from the additional 6 to 12 months to begin market roll out on the discrete implementation of your design needs to be considered as well. This extra cash from getting to market soon should be added onto the $150K to $250K being saved in design cost.

Conclusion

By using a SiP based processor system you should be able to simplify your product development while, at the same time, reduce its time to market. Although the amount of savings presented in this paper is only an estimate based on 100s of designs we and our customers have completed, a specific time savings resulting in your using a SiP should be determined based on your development experiences. By the way, as more of the system is integrated into a SiP, the shorter the development time line will become. It is our plan to not only integrate more of the system into the SiP, but to give you the ability to customize the SiP to meet your needs.

Want to stay up to date on the latest in SiP Technology? Sign up for our newsletter:

"*" indicates required fields