Masood Murtuza

Posted on March, 21, 2016

Categories

Recent Posts

- Octavo Systems Unveils the OSD32MP2 Series: Revolutionizing System Design in the Electronics Industry April 9, 2024

- Securing the Future: The Integral Role of SiP Technology in Thwarting Physical Attack Vectors in Embedded Systems March 12, 2024

- Developing Secure Embedded Systems: Best Practices and Strategies March 12, 2024

- Heterogeneous Integration (HI) and System-in-Package (SiP) Technology: A Comprehensive Overview February 20, 2024

- Understanding The Differences Between System-on-Chip (SoC), Package-on-Package (PoP), System-on-Module (SoM), and System-in-Package (SiP) January 17, 2024

SiP Metrics – Is there a Moore’s Law equivalent?

In the landmark paper of 1965, Gordon Moore[1] made an observation stating that with cost of manufacturing per device falling, it becomes economical to pack more and more devices in an IC chip. In his paper, Moore projected the number of devices in an IC chip would double every one to two years. This observation soon took the form of a proxy for future growth estimates in the semiconductor industry.

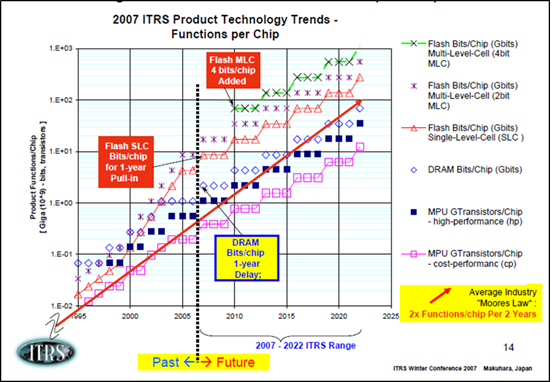

For decades, Moore’s law has been the benchmark for semiconductor technology development, eventually becoming a roadmap and a self-fulfilling prophecy for IC development. Figure 1[2] shows the growth of the number of devices in a semiconductor chip over time and tracks well with Moore’s projection.

The popularity of Moore’s law was in its simplicity. The number of transistors is a meaningful and simple measure and generally tracks with system development. However, Moore’s law is not universally applicable to all microelectronic devices. One such device is a SiP.

SiPs are emerging as a distinct class of microelectronic products because of their unique ability to integrate silicon of different process technologies such as Digital, Analog, Power, and DRAM as well as include passives and other devices to build integrated solutions. It is therefore useful to study SiP development and see if there are logical Moore’s Law like trends that are evident. In the next section, we will discuss a possible trend for SiPs, the reduction of external connections, and make a proposal for a growth metric for SiP technologies.

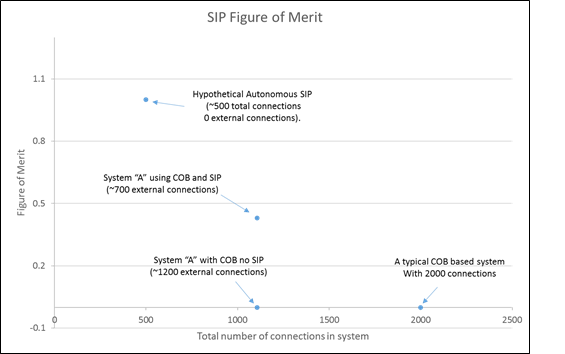

The ultimate goal of SiPs is to enable a fully integrated stand-alone autonomous electronic system. Such a SiP would have its own power supply, microprocessor, input, output and passive devices and be capable of performing the required function entirely with no external wired connection. An ideal SiP would have no external pins (if it had its own power source) or only have 2 pins – for power and ground. Since one of the purposes of a SiP is to reduce the number of wired connections we propose a figure of merit based on the reduction of these connections provided by using a SiP.

SiP “Figure of Merit” (FOM): One can define a FOM based on the number of externally wired connections in a SiP. If a SiP reduces the number of connections of the chips on board (COB) by half, then FOM is 0.5. If the SiP completely eliminates the need for external connections, therefore creating an autonomous system, then, in this ideal case, the FOM is 1. A system with no SiP means there was no reduction in interconnections to form a system. Such a system would have a FOM of 0. Therefore, FOM can be defined by the formula,

In the chart (Figure 2) below there are a few examples FOM. A real-life test case system “A” is also included for reference. In system “A” by using SiP the total number of interconnects dropped from about 1200 to 700 pins which gives a FOM of 0.42.

As discussed in a previous post, one of the key areas holding back the development of SiPs is the lack of a metric to measure their effectiveness and development. In this blog we have attempted to put forward a proposed metric tied to the reduction in number of external connections due to a SiP integration, which in turn correlates with the level of integration as a system. We will be using this metric to help demonstrate the value of our SiP devices.

We welcome your comments on this topic as we attempt to set a metric that can be used across the industry.

[1] Cramming more components onto integrated circuits, Gordon Moore, Electronics, Volume 38, Number 8, April 19, 1965

[2] International Technology Roadmap for Semiconductors (ITRS) 2007