Masood Murtuza

Posted on February, 15, 2016

Categories

Recent Posts

- Octavo Systems Unveils the OSD32MP2 Series: Revolutionizing System Design in the Electronics Industry April 9, 2024

- Securing the Future: The Integral Role of SiP Technology in Thwarting Physical Attack Vectors in Embedded Systems March 12, 2024

- Developing Secure Embedded Systems: Best Practices and Strategies March 12, 2024

- Heterogeneous Integration (HI) and System-in-Package (SiP) Technology: A Comprehensive Overview February 20, 2024

- Understanding The Differences Between System-on-Chip (SoC), Package-on-Package (PoP), System-on-Module (SoM), and System-in-Package (SiP) January 17, 2024

A Complementary Semiconductor Roadmap: System-In-Package (SiP) and the Challenges Ahead

Since the early 1960s, advances in semiconductor technology have been tracking Moore’s law. This “law”, based on a paper by Gordon Moore[i], states that the number of transistors per chip will double about every 18 months. For decades Moore’s law has been the overarching benchmark for development in the Semiconductor industry, especially in regards to System-On-Chip (SoC) development.

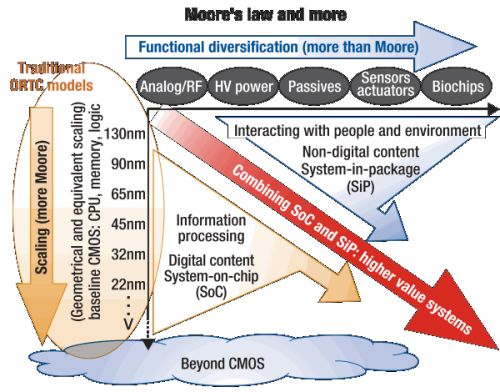

Moore’s law, however, is not endlessly sustainable (for reasons we discuss in this post) and an alternative approach was needed. Since the 2000’s there has been a recognition that System-In-Package devices (SiPs) indeed have a distinct role in semiconductor technology development. The 2009 ITRS (International Technology Roadmap for Semiconductors) on SiPs (Figure to the Right) reflects this recognition and outlines the technologies that are uniquely enabled by SiP technology. It is now becoming evident that SoC progression and Moore’s law cannot solely define the semiconductor roadmap and SiPs play a major and complementary role.

The 2009 ITRS (International Technology Roadmap for Semiconductors) on SiPs (Figure to the Right) reflects this recognition and outlines the technologies that are uniquely enabled by SiP technology. It is now becoming evident that SoC progression and Moore’s law cannot solely define the semiconductor roadmap and SiPs play a major and complementary role.

Will SiPs emulate the rapid advancements seen in SoCs? At Octavo we believe the answer is YES. We believe there are key areas for innovation to spur the wider and faster adoption of SiPs. Outlined below are a few of the challenges that we are working to address.

First, a meaningful metric for SiP progression similar to Moore’s law is required. A standardized metric will allow comparison and evaluation of SiP technologies to one another and compare solutions. Moore’s law simply uses the number of transistor in a chip as the metric. For System-in-Package the metric will have to be different and likely more complex. While it may include the number of transistors as with SoCs, extent of heterogeneous functional integration and the hierarchy of system integration achieved by SiP are some of the few factors that could be taken into consideration to define a meaningful metric. (We propose our metric in this post)

Secondly, SiP development will require development of supporting manufacturing infrastructure. SiPs by necessity will use most of the existing SoC manufacturing base which is not yet optimized for SiPs. This will bring many challenges[ii] to SiP development.

Here are a few of these challenges

- Supply chain management for constituent SoCs

- A uniform definition of known-good-die (KGD) between supplier and user

- Complexity of system design which includes passives, MEMs, and other non-traditional circuit elements

- Packaging and thermal management

- Functional testing

- Rapid prototyping and validation

- High volume manufacturing

- Reliability in unusual or harsh environments

Check back as we will dive into each of these challenges in the upcoming months. You can also sign up for our newsletter or follow us on Twitter, Facebook, or LinkedIn to get all of the latest news.

[i] Cramming more components onto integrated circuits, Gordon Moore, Electronics, Volume 38, Number 8, April 19, 1965

[ii] The road ahead for SiPs, Darvin Edwards & Masood Murtuza, Solid State Technology, Feb. 2011.