OSDZU3 System-in-Package

Performance and Flexibility of the AMD ZU3 MPSoC without the Complexity

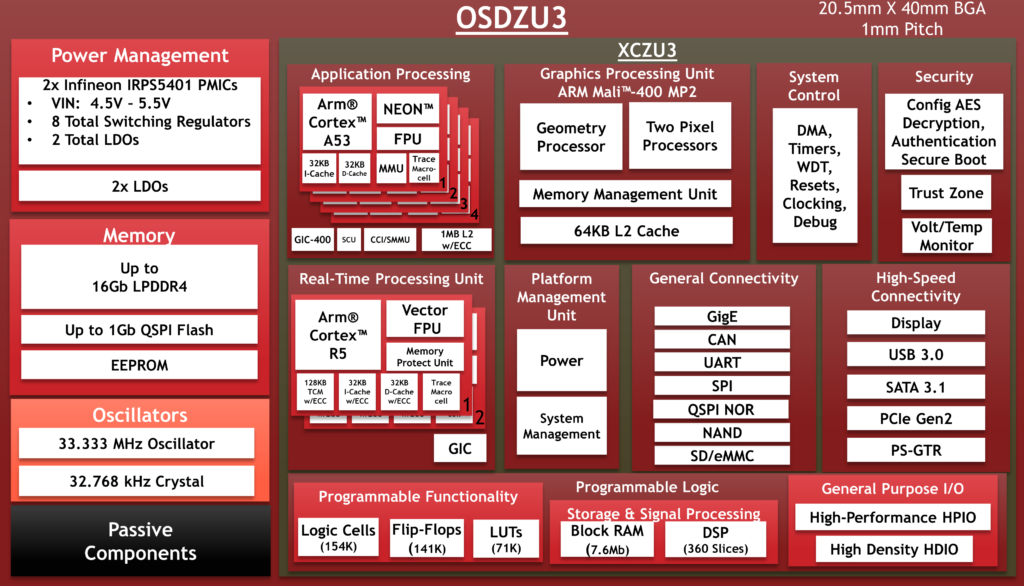

The OSDZU3 is the fastest and most flexible way to develop a system around the AMD Zynq® UltraScale+™ MPSoC. It allows you to harness the performance of the ZU3 MPSoC, while removing the complexities without sacrificing flexibility.

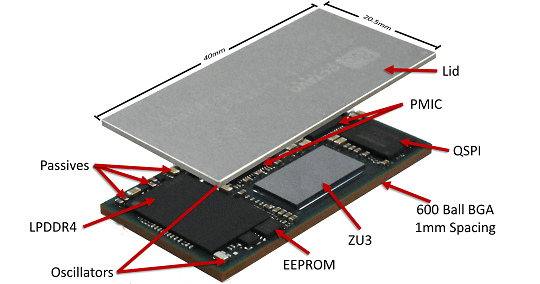

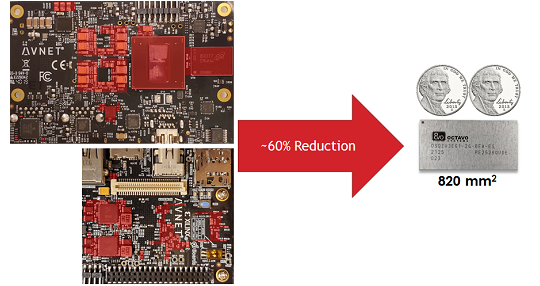

The OSDZU3 simplifies designs utilizing the AMD ZU3 Zynq UltraScale+ MPSoC by integrating a Power Management solution, LPDDR4 memory, QSPI memory, and other required components into a single BGA Package that is ~60% smaller than an implementation with discrete chip-down components. The integrated Power Management solution has been customized for the MPSoC and tailored to suit a large range of performance requirements. This integration significantly reduces Engineering time and effort spent on developing applications with ZU3 MPSoC, accelerating time to market by ~9 months and saving significant design costs.

Related Products

|

- OSDZU3 Schematic Check List – A guide that highlights key points that need to be checked in your schematic to ensure a successful design with the OSDZU3.

- OSDZU3 Layout Guide – A guide to help optimize the layout of your OSDZU3 based printed circuit board.

- OSDZU3 Thermal Guide – Application note that provides key thermal parameters for the OSDZU3

- OSDZU3 Power Guide – Application note that details the power system of the OSDZU3 and walks through an example of power budgeting a system using it.

- OSDZU3 to XCZU3 Pin Mapping Guide – Quick reference chart mapping pins of OSDZU3x System in Package and the XCZU3 processor

- OSDZU3 Vivado Guide – Application note that walks you through using Vivado with the OSDZU3.

- OSDZU3 Vitis Guide – Application note that walk you through using Vitis with the OSDZU3.

- OSDZU3 PMIC Programming Guide – Application note to validate and/or reprogram the behavior of the Integrated Infineon PMICs.

- Vitis AI Tutorial – A 4-part Acceleration tutorial series that will help you run Vitis-AI DPU-TRD based Face Detection demo, ADAS Detection demo (and other AI demos) on the OSDZU3-REF board.

| Product Number | Description | Price | Order From |

|---|---|---|---|

| OSDZU3EG1-2G-HFB | System-in-Package - ZU3EG -1, 2GB (16Gb) LPDDR4 x32, 32MB (256Mb) NOR QSPI, 4KB (32Kb) EEPROM, 2x Infineon IRPS5401 PMICs, 2x LDO, 33MHz Oscillator, 32KHz Oscillator, 1.8V Bank 500 (eMMC Boot), over 100 Passives - 20.5mm x 40mm, 600 Ball BGA, -40° to 100° C | Avnet Mouser Request a Quote | |

| OSDZU3EG1-2G-HFA | System-in-Package - ZU3EG -1, 2GB (16Gb) LPDDR4 x32, 32MB (256Mb) NOR QSPI, 4KB (32Kb) EEPROM, 2x Infineon IRPS5401 PMICs, 2x LDO, 33MHz Oscillator, 32KHz Oscillator, 3.3V Bank 500 (No eMMC Boot), over 100 Passives - 20.5mm x 40mm, 600 Ball BGA, -40° to 100° C | Avnet Mouser Request a Quote | |

| OSDZU3EG1-2G-BFB | System-in-Package - ZU3EG -1, 2GB (16Gb) LPDDR4 x32, 32MB (256Mb) NOR QSPI, 4KB (32Kb) EEPROM, 2x Infineon IRPS5401 PMICs, 2x LDO, 33MHz Oscillator, 32KHz Oscillator, 1.8V Bank 500 (eMMC Boot), over 100 Passives - 20.5mm x 40mm, 600 Ball BGA, 0° to 85° C | Avnet Mouser Request a Quote | |

| OSDZU3EG1-2G-BFA | System-in-Package - ZU3EG -1, 2GB (16Gb) LPDDR4 x32, 32MB (256Mb) NOR QSPI, 4KB (32Kb) EEPROM, 2x Infineon IRPS5401 PMICs, 2x LDO, 33MHz Oscillator, 32KHz Oscillator, 3.3V Bank 500 (No eMMC Boot), over 100 Passives - 20.5mm x 40mm, 600 Ball BGA, 0° to 85° C | Avnet Mouser Request a Quote | |

| OSDZU3EG1-2G-IFB | System-in-Package - ZU3EG -1, 2GB (16Gb) LPDDR4 x32, 32MB (256Mb) NOR QSPI, 4KB (32Kb) EEPROM, 2x Infineon IRPS5401 PMICs, 2x LDO, 33MHz Oscillator, 32KHz Oscillator, 1.8V Bank 500 (eMMC Boot), over 100 Passives - 20.5mm x 40mm, 600 Ball BGA, -40° to 85° C | Avnet Mouser Request a Quote | |

| OSDZU3EG1-2G-IFA | System-in-Package - ZU3EG -1, 2GB (16Gb) LPDDR4 x32, 32MB (256Mb) NOR QSPI, 4KB (32Kb) EEPROM, 2x Infineon IRPS5401 PMICs, 2x LDO, 33MHz Oscillator, 32KHz Oscillator, 3.3V Bank 500 (No eMMC Boot), over 100 Passives - 20.5mm x 40mm, 600 Ball BGA, -40° to 85° C | Avnet Mouser Request a Quote |

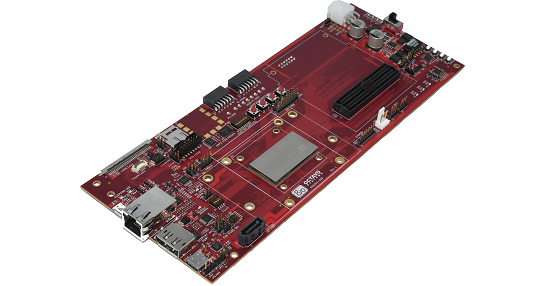

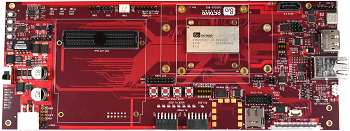

OSDZU3-REF

The Octavo Systems OSDZU3-REF is a full featured 4-layer development platform for the OSDZU3 System-in-Package devices. Based on the UltraZED PCIe Carrier Card from Avnet the OSDZU3-REF provides access to a host of peripherals and expansion headers to fully evaluate the OSDZU3 in your application. Its USB-C, USB 3.0, SATA Host, and 1Gb Ethernet interfaces support easy connectivity to off the shelf peripherals. It can also be expanded with custom functionality through the FMC Low Pin Count Connector and the PMOD headers. The OSDZU3-REF also supports displays through a Display Port or LVDS Display + Touch Interface. It is pre-installed with a Peta Linux Distribution, provided by DesignLinx, that features a number of demo applications, enabling you to go from box to AI demo in a matter of minutes.

The Octavo Systems OSDZU3-REF is a full featured 4-layer development platform for the OSDZU3 System-in-Package devices. Based on the UltraZED PCIe Carrier Card from Avnet the OSDZU3-REF provides access to a host of peripherals and expansion headers to fully evaluate the OSDZU3 in your application. Its USB-C, USB 3.0, SATA Host, and 1Gb Ethernet interfaces support easy connectivity to off the shelf peripherals. It can also be expanded with custom functionality through the FMC Low Pin Count Connector and the PMOD headers. The OSDZU3-REF also supports displays through a Display Port or LVDS Display + Touch Interface. It is pre-installed with a Peta Linux Distribution, provided by DesignLinx, that features a number of demo applications, enabling you to go from box to AI demo in a matter of minutes.

The OSDZU3-REF is the perfect platform to evaluate the capabilities of the OSDZU3 System-in-Package in your next application.

Together with our partner DesignLinx we are ensuring the OSDZU3 is completely compatible with all AMD tools and software for the UltraScale+ MPSoC devices. (Login is required)

Hardware Files

Board Support Packages

* The OSDZU3 BSP 2023.1 uses the traditional sysvinit init system and does not fully support the Weston Windowing system. This may cause display glitches like trailing cursor/windows on DP or LVDS outputs. There is a suggested work around that requires applying patches and moving from sysvinit to systemd, however, this has not been verified.

To make designing with Octavo Systems devices easier, a number of schematic symbol libraries have been provided below. There are options for a variety of schematic capture and layout programs. Please choose the one that best suits your needs.