Related Products

OSD335x C-SiP, the AM335x System in Package, Power Application Note

Published On: March, 22, 2019 By: Eshtaartha Basu | Updated: September 3, 2019 by Cathleen Wicks

The C-SiP, the complete AM335x System in Package, power application note is intended for engineers to understand the power management system of OSD335x C-SiP system in package. The C-SiP power application note is also intended to aid in power budgeting for systems using the OSD335x C-SiP. The C-SiP power application note provides an overview of the power management system inside the OSD335x C-SiP and runs through an example application power budgeting procedure.

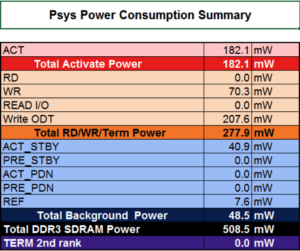

The OSD335x C-SiP system in package contains the TPS65217C Power Management Integrated Circuit (PMIC) and the TL5209 Low Drop-Out (LDO) regulator as well as all associated passives for power management. The PMIC is responsible for powering the AM335x processor, DDR3, eMMC, EEPROM as well as provide output power for other system needs. It provides configurable power-up and power-down sequencing required by the processor and monitors the processor input voltage levels. The PMIC contains 3 DC-DC power converters, 2 LDOs and 2 load switches that can be configured as LDOs that can be used as power supplies. It can be powered by any combination of a 5V AC adapter, USB port, or Single Cell Li-Ion battery. Figure 1 shows the power system of OSD335x C-SiP including connections between the PMIC and various power domains of the processor.

Table 1 shows the voltage output levels of each of the voltage sources. Each of the output voltages can be changed dynamically using I2C commands when the PMIC is in active mode.

| TPS65217C Voltage Source | OSD335x Voltage rail | Voltage (V) |

| DCDC1 | VDDS_DDR | 1.5 |

| DCDC2 | VDD_MPU | 1.1 |

| DCDC3 | VDD_CORE | 1.1 |

| LDO1 | SYS_RTC_1P8V | 1.8 |

| LDO2 | SYS_VDD2_3P3V | 3.3 |

| LDO3 | SYS_VDD_1P8V | 1.8 |

| LDO4 | SYS_VDD3_3P3V | 3.3 |

Table of Contents

1.Introduction

2.Power Up Sequence

2.1.Additional Functions of the PMIC

3.Power Design Considerations

3.1Inrush

3.2Rise Time

4.Power Budgeting: How to Approach It

4.1Step 1: Creating a Power Diagram

4.2Step 2: Creating a Power Budget

4.2.1Maximum Power

4.2.2Redefining the Power Budget

4.3Step 3: Tally Up

5.Conclusion

6.Reference Documents

7.Revision History

![]() A PDF version of this App Note can be found here.

A PDF version of this App Note can be found here.

2 Power Up Sequence for the OSD335x C-SiP, the AM335x System in Package

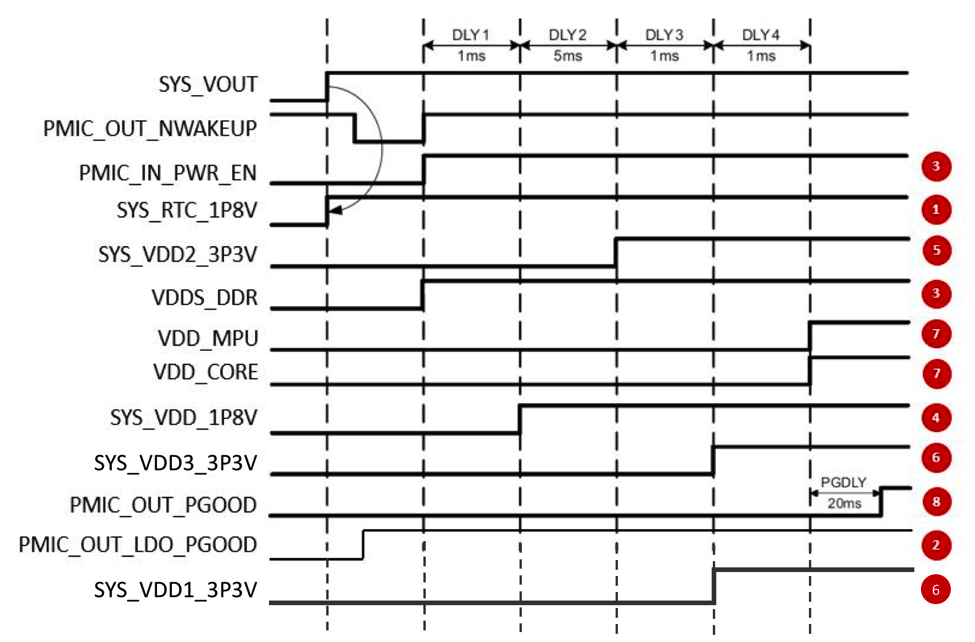

The power-up sequence of the processor is shown below in Figure 2, with the numbers in red representing the order in which they come up, and the main power up events are described below:

- SYS_RTC_1P8V is activated.

- PMIC_OUT_LDO_PGOOD rail which is connected externally to the processor’s RTC_PWRONRSTN (Power on reset of RTC domain) is pulled high to indicate presence of right voltages for the RTC domain of the processor to power-up.

- RTC circuitry in the processor comes up and pulls the PMIC_IN_PWR_EN signal high instructing the PMIC to start power-up sequence. The output of DCDC1 (VDDS_DDR) which powers the DDR memory is also activated.

- Output of LDO3 (SYS_VDD_1P8V) is activated

- Output of LDO2 (SYS_VDD2_3P3V) is activated

- Output of LDO4 (SYS_VDD3_3P3V) is activated. SYS_VDD3_3P3V rail also enables the TL5209 LDO which instantaneously brings up the SYS_VDD1_3P3V (TL5209 datasheet)

- Outputs of DCDC2 (VDD_MPU) and DCDC3 (VDD_CORE) are activated

- PMIC_OUT_PGOOD which is connected externally to the processor’s PWRONRSTN (Power on reset of AM335x) of the processor is pulled high releasing the processor from reset.

This power up sequence and delays between each step of the sequence are already programmed into the PMIC inside the OSD335x C-SiP so you don’t need to worry about it. The power-down sequence follows the reverse order of the power-up sequence.

2.1 Additional Functions of the PMIC

The PMIC also performs some tertiary functions. A few of the key functions are listed below. For a complete explanation of all the functions provided by the TPS65217C PMIC refer to the datasheet.

- The PMIC retrieves the processor from OFF or SLEEP mode upon detecting a falling edge on PMIC_IN_PB_IN. It also power cycles the processor if PMIC_IN_PB_IN is held low for more than 8 seconds.

- It provides an active low wake up signal (PMIC_OUT_NWAKEUP) which is de-asserted when a wakeup event is detected.

- The PMIC has an interrupt pin (PMIC_OUT_NINT) to signal an event or fault condition to the processor. The pin is released when the processor reads the INT register.

- PMIC provides a linear charger for Single Cell Li-Ion batteries and allows charging of the battery and powering of the system at the same More information can be obtained from the datasheet.

- The TPS65217C provides protection to the AM335x and itself in the event of catastrophic situations like an unexpected short or excessive current leakage.

- It monitors the functioning of a battery if one is connected and charges the battery when possible.

Now that the function and of the PMIC and its relationship with the processor is clear, the process of power budgeting discussed below can be better understood.

3 Power Design Considerations

Some important considerations that need to be satisfied for the system to power up without issues are given below:

- Inrush current

- Rise time of input voltage

Each of these considerations in terms of the OSD335x C-SiP are discussed below:

3.1 Inrush:

Inrush current is the maximum instantaneous input current drawn by a system during power up. This instantaneous current can be much higher than the steady state current the system consumes.

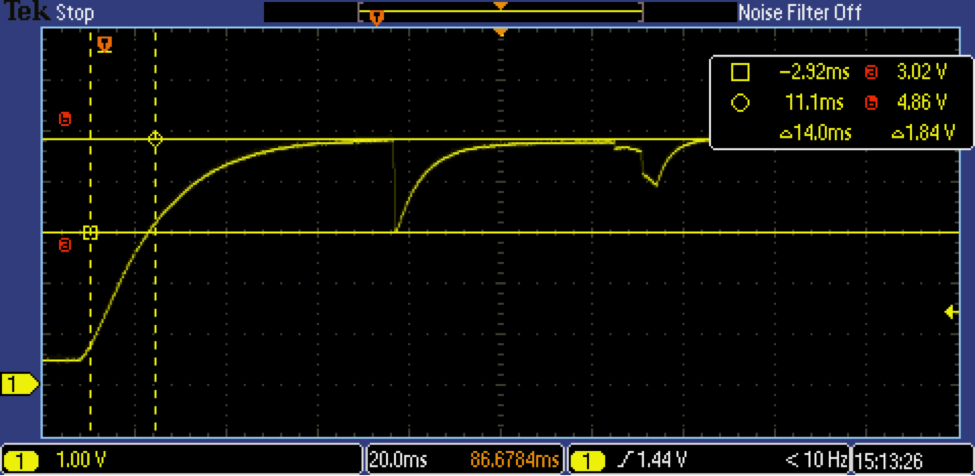

For the OSD335x family, the TPS65217C PMIC manages the power supplies to the processor and connected output power rails. The inrush occurs at 55ms after input power is activated. The following figure shows a bad power up when the input power rail is unable to sustain the specified operating conditions.

So, design choices have to made to mitigate such a fault condition. Two factors that affect inrush behavior are the input power supply capacity and the bypass capacitance. First, the current capacity of the power supply used to power the system must exceed the inrush current of the system. Although inrush current is specific to a system, typical inrush current measurements for the OSD335x family is given below:

be changed dynamically using I2C commands when the PMIC is in active mode.

| Power Input | Inrush Current (mA) |

| VIN_AC | 1500 |

| VIN_USB | 500 |

In addition to the current capacity of power source, bypass capacitance on the output power rail (SYS_VOUT) that powers the processor and other downstream components will help stabilize the inrush effects. It is recommended to have >47uF bypass capacitance on SYS_VOUT rail.

3.2 Rise Time

The PMIC has certain thresholds for detection of a power on event. One of the power-on events is the positive edge on a power input rail (VIN_AC or VIN_USB). The rise time, which is defined as the time taken by the power rail to go from 100mV to 4.5V, needs to be <50ms for the PMIC to trigger a power on event. So, the power supply used to power the system needs to satisfy this condition.

4. Power Budgeting: How to Approach It

It is a good practice to make a power budget for your product/design at the beginning of the project. Good power budgeting contributes to circuit robustness, increased product life and reduced cost of the product. A power budget should include the availability of power, operating temperature, amount of data collected, communication, and operation modes of the processor.

4.1 Step 1: Creating a Power Diagram

The first step in making a power budget is to have a power diagram that shows all the power paths of the system. Start with all the available power sources for the system. For OSD335x C-SiP, this would include power rails that are described in the datasheet as output power supplies. There are seven output power rails on the OSD335x C-SiP including a 2.75V – 5.5 output (SYS_VOUT), three 3.3V outputs (SYS_VDD1_3P3V, SYS_VDD2_3P3V and SYS_VDD3_3P3V) and three 1.8V outputs (SYS_RTC_1P8V, SYS_VDD_1P8V and SYS_ADC_1P8V).

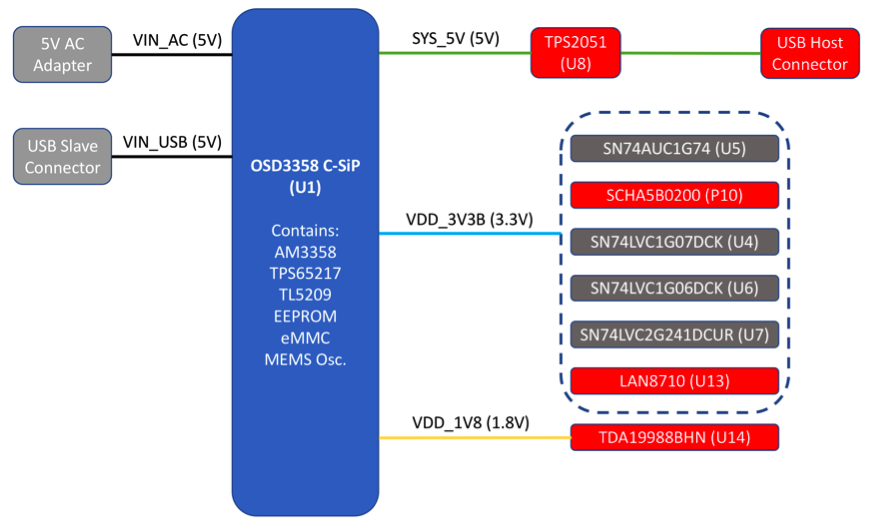

Next, put in the power consuming components and connect them to the appropriate power rail. The connection should be based on the voltage input level for the component. Current supply capacities of the power rails and ease of use can also be factors for choosing the best power rail for the component. In order to understand this process, let us use the SBC reference design board that uses the OSD335x. The board provides access to many peripherals of OSD335x (OSD335x Datasheet) and has a number of external components powered by the OSD335x. The OSD335x is similar to OSD335x C-SiP but it does not integrate eMMC, EEPROM and 24MHz oscillator within the SiP. Hence, these components are connected externally to the SiP in SBC reference design. Whereas, these components are internal to the OSD335x C-SiP (OSD335x C-SiP Datasheet). However, power consumption figures mostly remain the same irrespective of whether OSD335x or OSD335x C-SiP is used in the case of SBC reference design. Therefore, it can be used as an example for the C-SiP power analysis. Figure 3 shows the completed power system diagram for the design. It shows most of the components that draw at least a nominal amount of power.

The diagram not only shows the power rail for a particular component but also lists all the components that are being powered by a power rail. In addition to helping with the power budgeting, this allows you to identify power issues early in the design process and make necessary adjustments.

4.2 Step 2: Creating a Power Budget

The next step involves making a power budget to estimate power consumption of each component and thus the total power consumption of the board.

4.2.1 Maximum Power

There are several challenges involved in accurately estimating the power consumption of each component. For example, it is difficult to estimate how much current, the AM3358 processor and the DDR Memory draw since that is highly application specific. Power consumption will also depend on the presence of a USB device or a Micro SD card. To account for all situations, we can start out by assuming maximum power consumption for all the components. Table 2 shows the power budget table for OSD3358 SBC Reference Design assuming maximum power consumption for each component.

| Part Name | Part Number | Max Current (mA) | Supply voltage | Rail Voltage (V) | Max Power (mW) |

| AM3358 | U1 | 307.8 | Internal | 5 | 1539 |

| TPS65217C | U1 | < 1 | Internal | 5 | <5 |

| TL5209 | U1 | 25 | Internal | 5 | 125 |

| DDR RAM | U1 | 339 | Internal | 1.5 | 508.5 |

| TPS2051 | U8 | < 1 | SYS_VOUT | 5 | < 5 |

| USB Connector | P3 | < 500 | SYS_VOUT | 5 | < 2500 |

| 24LC32AT | U1 | 3 | SYS_VDD1_3P3V (Internal) | 3.3 | 15 |

| SN74AUC1G74 | U5 | 9 | SYS_VDD1_3P3V | 3.3 | 45 |

| 24MHz Oscillator* | U1 | 5 | SYS_VDD1_3P3V (Internal) | 3.3 | 25 |

| SCHA5B0200 | P10 | 200 | SYS_VDD1_3P3V | 3.3 | 1000 |

| eMMC** | U1 | 200 | SYS_VDD1_3P3V (Internal) | 3.3 | 1000 |

| SN74LVC1G07DCK | U4 | 2 | SYS_VDD1_3P3V | 3.3 | 10 |

| SN74LVC1G06DCK | U6 | 2 | SYS_VDD1_3P3V | 3.3 | 10 |

| SN74LVC2G241DCUR | U7 | 24 | SYS_VDD1_3P3V | 3.3 | 120 |

| LAN8710 | U13 | 53.1 | SYS_VDD1_3P3V | 3.3 | 265.5 |

| TDA19988BHN | U14 | 77 | SYS_VDD_1P8V | 1.8 | 385 |

| Total | ~7558 |

* The oscillator max current consumption is found in the OSD3358 C-SiP datasheet.

** The eMMC max current consumption can be estimated from the OSD3358 C-SiP datasheet

*** The SYS_VDD1_3P3V output rail is internally powered by TL5209 LDO which consumes 5V from SYS_VOUT. Similarly, the SYS_VDD_1P8V output rail is internally powered by the TPS65217C LDO3 which consumes 5V from SYS_VOUT. Hence, in power calculations for this voltage rail, 5V is used for voltage instead of 3.3V or 1.8V.

Maximum current consumption values can be found from the component datasheets for most devices. However, as mentioned earlier there is no deterministic way of calculating the current consumed by the AM335x and the DDR3 as they are highly application specific. The next two sections will explore how to use tools provided by TI and Micron to estimate the max power used by the AM335x and DDR.

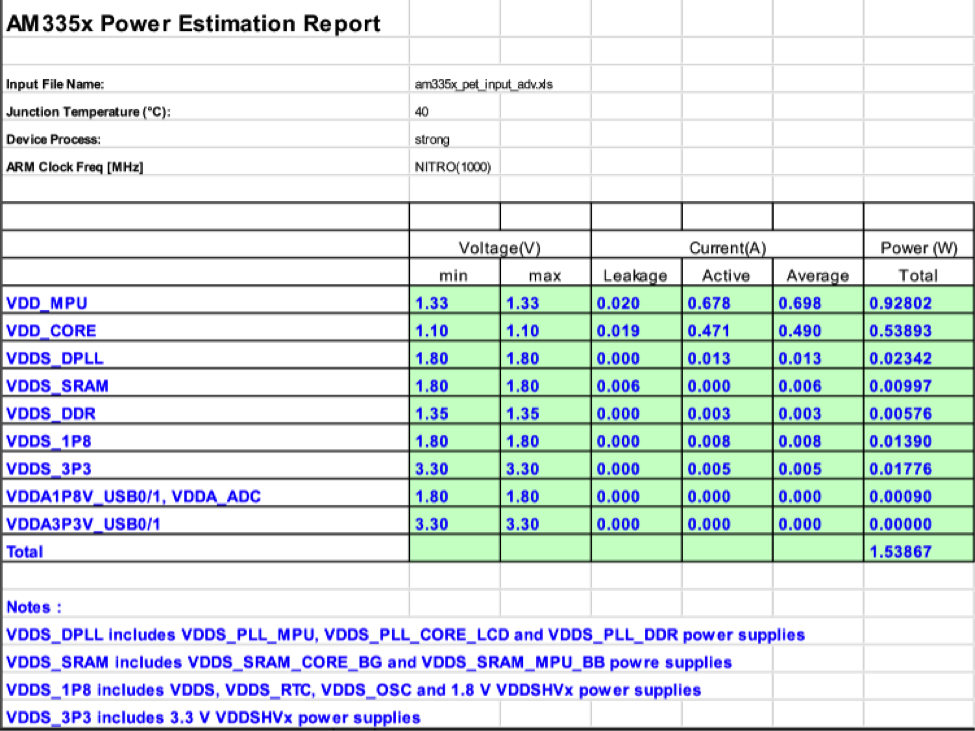

4.2.1.1 Using Power Estimation Tool for estimating AM3358 power consumption

Texas Instruments provides access to a power estimation tool that can calculate the internal power consumption of AM3358 including individual power domains of the processor. The process involves filling out a spreadsheet and submitting it to a webpage. The detailed procedure is described in the wiki page “AM335x Power Estimation Tool”. A short overview of the process with notes on usage with the OSD335x C-SiP is given below. The inputs shown in the screenshots were put in to calculate the maximum power consumption of AM335x.

- Download either the simplified or the advanced spreadsheet for AM335x from http://www.ti.com/tool/powerest

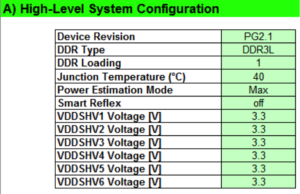

- In section A, among other inputs, set the device revision to PG2.1, DDR type to “DDR3L”, DDR loading to 1, and all the VDDSHVx voltages to 3.3. The power modes of AM335x are discussed later in this document.

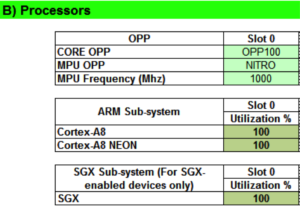

Figure 5: System configuration in power estimation spreadsheet - Set the Operational Performance Point (OPP), MPU frequency and Utilization percentages in Section B.

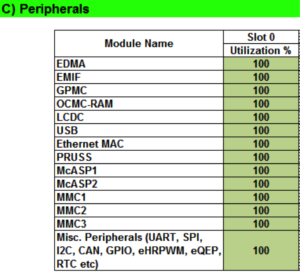

Figure 6: Processor options and utilization in power estimation spreadsheet - Input Utilization percentages for peripheral usage of AM335x in section C.

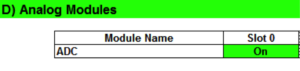

Figure 7: Peripheral utilization in power estimation spreadsheet - Enable/Disable analog modules in Section D.

Figure 8: ADC module usage in power estimation spreadsheet - Click on the submit button in the spreadsheet. This will open a webpage to which the edited spreadsheet can be uploaded to. This requires logging in to TI’s website.

- A power analysis report will be emailed to the email address attached to the user account logged into.

The worst-case current consumption can be obtained by maximizing the inputs to the spreadsheet. Other relevant resources that help estimation of AM335x power usage are given below:

4.2.1.2 Estimating Power for the DDR3

Like the AM335x spreadsheet, Micron provides a spreadsheet to estimate DDR3L power consumption. Though the exact power consumption depends on the part number of the memory, the spreadsheet serves as a rough estimation tool. A brief use case of the spreadsheet is shown below.

- Download the spreadsheet available for the DDR3L memory on Micron’s website.

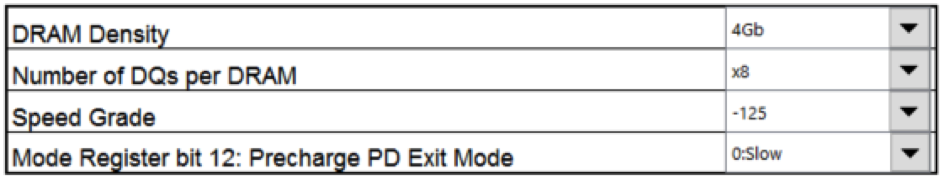

- Input SDRAM configuration inputs in the “DDR3 Config” The screenshot shows inputs specific to DDR3 memory used in OSD335x C-SiP.

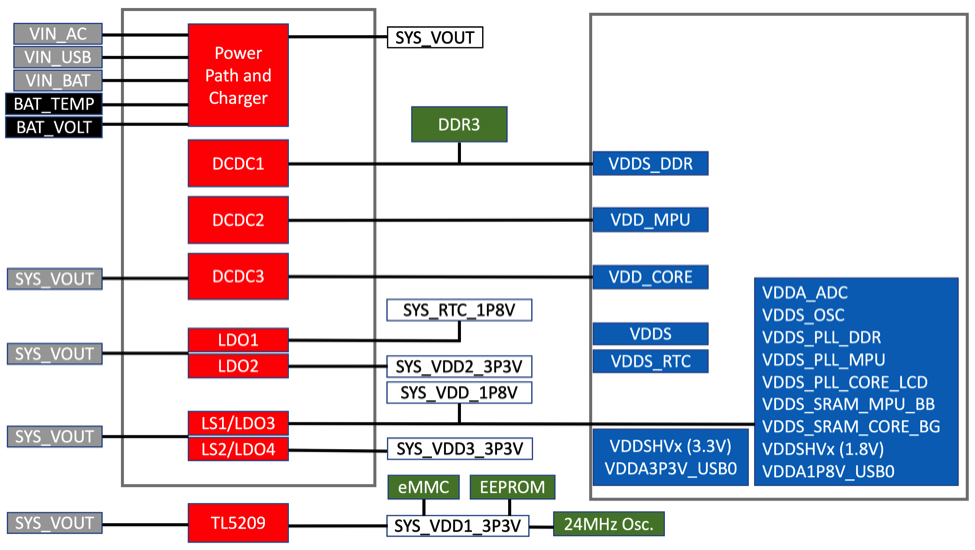

Figure 10: DDR3 configuration in power estimation spreadsheet - Input DRAM usage conditions in “System Config” These inputs may vary based on use case. The inputs shown below are for estimating worst case power consumption of the RAM.

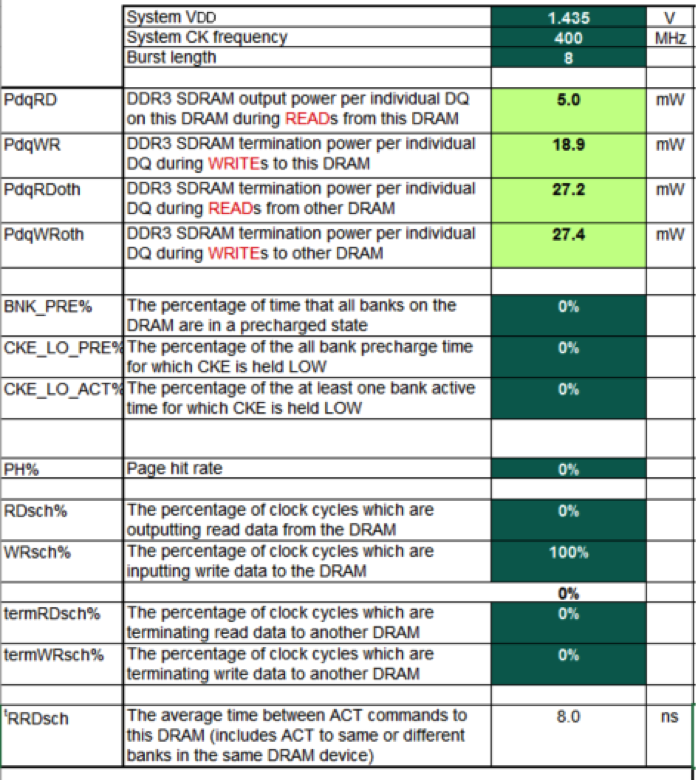

Figure 11: DDR3 system configuration in power estimation spreadsheet - The “Summary” page will show the power consumption summary for previously entered inputs.

Figure 12: DDR3 power consumption summary From the results, the worst case current consumption was calculated to be 339 mA with 1.5 V input

4.2.2 Refining the Power Budget

Some of the current consumption numbers are highly unrealistic. No system uses all the processor cores and peripherals at 100% utilization. The DDR current consumption is calculated assuming 100% of the time is spent writing to the memory with lowest ACT command interval. So, while it is safe to use these figures to assume worst-case load, the system would be vastly over-designed. It is better to build another power budget table with typical current consumptions and a more application specific scenario while keeping the previous version in mind.

| Part Name | Part Number | Max Current (mA) | Supply Voltage | Rail Voltage (V) | Max Power (mW) |

| AM3358 | U1 | 186.4 | Internal | 5 | 932 |

| TPS65217C | U1 | < 1 | Internal | 5 | <5 |

| TL5209 | U1 | 8 | Internal | 5 | 40 |

| DDR RAM | U1 | 206 | Internal | 1.5 | 309 |

| TPS2051 | U8 | < 1 | SYS_VOUT | 5 | < 5 |

| USB Connector | P3 | < 500 | SYS_VOUT | 5 | < 2500 |

| 24LC32AT | U1 | 1 | SYS_VDD1_3P3V (Internal) | 3.3 | 5 |

| SCHA5B0200 | P10 | 100 | SYS_VDD1_3P3V | 3.3 | 500 |

| eMMC | U1 | 80 | SYS_VDD1_3P3V (Internal) | 3.3 | 400 |

| SN74LVC1G07DCK | U4 | 1 | SYS_VDD1_3P3V | 3.3 | 5 |

| SN74LVC1G06DCK | U6 | 1 | SYS_VDD1_3P3V | 3.3 | 5 |

| SN74LVC2G241DCUR | U7 | 16 | SYS_VDD1_3P3V | 3.3 | 80 |

| Total | 4786 |

*** SYS_VDD1_3P3V output rail is internally powered by TL5209 LDO which consumes 5V from SYS_5V. Hence, in power calculations for this voltage rail, 5V is used for voltage instead of 3.3V.

Table 3 shows an application specific power budget table in which the processor is operated in conditions described in Table 4. All the other peripherals and features are assumed to be disabled in this scenario and ‘typical’ current consumption values from component datasheets are used rather than ‘maximum’ current consumption values.

| Feature/peripheral | Utilization (%) |

| Cortex A8 | 70 |

| Cortex A8 NEON | 70 |

| CORE OPP | OPP100 |

| MPU OPP | NITRO |

| MPU Frequency | 1 GHz |

| EMIF | 70 |

| OCMC RAM | 70 |

| USB | 70 |

| Ethernet MAC | 70 |

| MMC1 | 70 |

| Miscellaneous Peripherals | 50 |

| ADC | OFF |

Note that the utilization percentages of each feature/peripheral of the AM335x processor are still high. This is done to leave ourselves some head room if the board runs into an unexpected scenario. Similarly, the RAM usage is also safely assumed to have a 20% page hit rate, a 10ns interval between ACT commands, 30% of the time spent reading from RAM and 30% of the time writing to the RAM. Also, observe that several components of the board are not in use and so are left out of Table 3.

4.3 Step 3: Tally Up

Thus, we have an extreme scenario and an application specific application scenario for our power budget. The usage scenarios should now be stacked up to the supply capacities of output power rails of OSD335x C-SiP that we outlined in step 1 to make sure everything checks out. Given below are the conditions that need to be verified and corresponding usage on the OSD3358 SBC reference design from the datasheet:

| Condition | Limitation | Extreme | Application |

| VIN_AC input current | 2.0 A | 1.44 A | 1.00 A |

| VIN_USB input current* (See below) | 1.3 A | 1.44 A | 1.00 A |

| VIN_BAT input current (5V battery) | 2.0 A | 1.44 A | 1.00 A |

| SYS_VOUT output current | 500 mA | 500mA | 500mA |

| SYS_VDD1_3P3V output current | 500 mA | 423.1mA | 229mA |

| SYS_VDD2_3P3V (VDD_3V3AUX) output current | 100 mA | – | – |

| SYS_RTC_1P8V (VDD_RTC) output current | 100 mA | – | – |

| SYS_VDD_1P8V (VDD_1V8) output current | 250 mA | 77mA | – |

| SYS_ADC_1P8V (VDD_ADC) output current | 25 mA | – | – |

From Table 5, although SYS_VOUT current consumption looks like it touches the maximum recommended output current, it is highly unlikely to have a USB device that would draw 500mA in the application. The extreme condition input current does exceed the USB input current limit. But, there are alternative input power paths (AC and BAT) that can mitigate this issue in spite of the fact that the scenario will not occur. All the application specific current draws are significantly lower than the limits. So, there is enough room for the board to be able to deal with unexpected situations of high current

While this board presents no problems in power analysis, there might be situations where the current draws are close or exceed the power rail limits in a design. In this case, alternative approaches to design can solve the problem. The OSD335x C-SiP has multiple rails of 1.8V and 3.3V. So, spreading out the total current consumption of all the parts among the available power rails can be a first approach. If that does not solve the issue, alternative power paths need to be designed. This might involve using more regulators and/or using AC/BAT input instead of the current limiting USB input.

5 Conclusion

This document discussed the power management system of OSD335x C-SiP and presented a power budgeting procedure that helps in efficient product design. Most of the above discussion centers around hardware. However, software also plays an important role in power management. Some aspects of software power management and a case study on its advantages are presented in part 2 of this document.

6 Reference Documents

- TPS65217C datasheet

- TL5209 LDO datasheet

- AM335x datasheet

- Powering the AM335x with TPS65217C

- Using Power Estimation Tool to estimate power consumption of AM335x

- Processor SDK Linux kernel performance guide

- AM335x power consumption summary

- Spreadsheet for DDR3 power consumption estimation

- AM335x Power Management User Guide

- Linux Core Power Management User’s guide

- AM335x Power Management User Guide

- AM335x Power Management Standby User’s Guide

7 Revision History

| Revision Number | Revision Date | Changes | Author |

|---|---|---|---|

| 1 | 3/15/2019 | Initial Release | E. Basu |