Related Products

OSD32MP15x Layout Guide

Published On: February, 25, 2019 By: Eshtaartha Basu | Updated: August 6, 2020 by Greg Sheridan

The OSD32MP15x , the STM32MP1 System in Package, was designed to minimize the number of Printed Circuit Board (PCB) layers and make the layout process easy. This document will cover important aspects of PCB layout design specific to the OSD32MP15x and help designers quickly begin the PCB layout process. First, this document will discuss the layout of the OSD32MP15x BGA. Then it will discuss a few common layout scenarios using relevant examples with recommendations on pours for Power, Ground and other supporting circuitry.

This document assumes that the reader is already familiar with layout design process and the OSD32MP15x (OSD32MP15x Data Sheet), the STM32MP1 System in Package. The document should not be used as a comprehensive layout tutorial or a generic layout design guide.

Table of Contents

1.Introduction

2.OSD32MP15x Layout Specifications

2.1 Background Information

2.2 Ball Function Map

2.3 Footprint Configuration

3. Routing and Vias

3.1 Trace Size Background Information

3.1.1 Example: 5/5 Traces Routed Between Pads of the OSD32MP15x

3.2 Via Size Background Information

3.2.1 Example: A 12/24 via between 4 pads of the OSD32MP15x

3.2.2 Example: 3.2.2 Example: A 10/18 via and 5/5 trace between 4 pads of the OSD32MP15x

3.2.3 Example: Two 10/16 vias between 4 pads of the OSD32MP15x

4. OSD32MP15x Layout Examples

4.1Signal Pin Fanout

4.2Power Inputs

43 Power Outputs

4.4Ground Connections

5. References

6.Revision History of this Document

2 OSD32MP15x Layout Specifications

The OSD32MP15x Family of System-In-Package (SiP) products are building blocks designed to allow easy and cost-effective implementation of systems based on ST’s dual core Cortex-A7 line of processors. The OSD32MP15x, the STM32MP1 System in Package, integrates the STM32MP157C processor along with the STPMU1 PMIC, up to 1 Gigabyte (GB) of DDR3 Memory, a 4 Kilobyte (KB) EEPROM for non-volatile configuration storage and resistors, capacitors, and inductors into a single 18mm x 18mm design-in-ready package.

This section will introduce important specifications, ball mapping and footprint information of the OSD32MP15x.

2.1 Background Information

To understand layout guidelines and methodology used for the recommendations made in this document in more detail, please refer to the following documents:

2.2 Ball Function Map

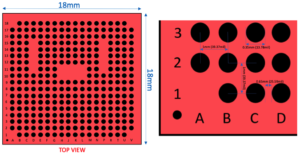

The Ball function map shown in Figure 1 provides a visual representation of the arrangement of the pins (Top View) of the OSD32MP15x. This can help with the placement and orientation of the OSD32MP15x in a design.

3.3 Footprint Configuration

The OSD32MP15x footprint parameters are shown in Figure 2 (Top View) and listed in Table 1.

| Parameter | Value |

| Package Dimension | 18mm x 18mm x 1.85mm |

| Number of Balls | 302 |

| Ball Grid | 18 rows x 18 columns |

| Ball Pitch | 1mm (39.37mils) |

| Landing Pad Size | 0.35mm (13.78 mils) |

The landing pad size was determined from the IPC-7351A specification. To find more information about IPC-7351A specifications, refer BGA Ball Pad Size section of BGA PCB Design document from Texas Instruments (TI).

For more information on the footprint configuration, please see the Mechanical Dimensions section of the OSD32MP15x datasheet.

3 Routing and Vias

When pricing a PCB, the size of the traces and vias directly affect the cost to manufacture the board. However, larger traces and vias, while cheaper, can make layout more difficult. Therefore, it is necessary to understand the optimum size of traces and vias for a given design. This section will provide background information on trace and via sizes and discuss layout tradeoffs when designing with the OSD32MP15x BGA.

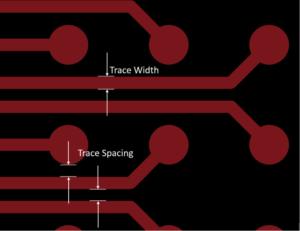

3.1 Trace Size Background Information

The number of traces that can pass between any two pads of a BGA footprint depends on the trace width and trace spacing. Trace width is the actual width of the trace. Trace spacing is the distance between the edges of any two adjacent traces or a trace and a pad. Trace width and trace spacing are shown pictorially in Figure 3.

In this document, a “x/y trace” indicates a PCB that uses design rules with trace width of x mils and trace spacing of y mils. For example, a 5/6 trace indicates a PCB with trace width of 5mils and trace spacing of 6mils.

The number of traces that can be routed between any two adjacent pads of the BGA can be calculated using the formula (formula assumes all the traces are equal width):

tn tw + (tn + 1) ts <= BP – BD

where,

tn = number of traces

tw = trace width

ts = trace spacing

BP = BGA pitch

BD = BGA ball diameter

For example, to calculate the number of 5/5 traces that can be routed between adjacent pads of the OSD32MP15x BGA: tw = 5mils, ts = 5mils, BP = 39.37mil (1mm) and BD = 13.78mil (0.35mm)

Using all this in the above equation:

5tn + 5(tn + 1) <= 25.59

10tn <= 20.59

tn <= 2.059 traces.

This result indicates that two (2) full 5/5 traces can be routed between adjacent balls of the OSD32MP15x BGA. Similarly, the number of traces can be calculated for other routing rules, see Table 2. In the OSD32MP15x BGA, almost all signal pins are in the first three rows / columns of the BGA. This means to fully escape the BGA, only 2 traces are needed to be routed between each pair of pads. See Section 4.1 for more details on OSD32MP15x fanout.

| Trace width(mils) / Trace spacing(mils) | Number of traces between two adjacent BGA pads |

| Larger than 5/5 | 1 |

| 5/5 | 2 |

| 3.65/3.65 or smaller | 3 or more |

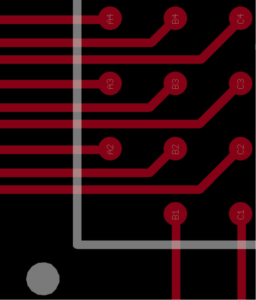

3.1.1 Example: 5/5 Traces Routed Between Pads of the OSD32MP15x

On all sides, the first three rows of OSD32MP15x can be easily accessed using 5/5 traces as shown in Figure 4.

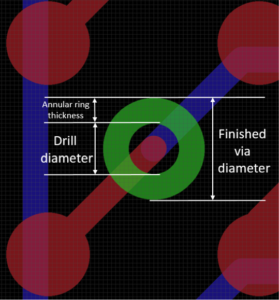

3.2 Via Size Background Information

There are two important parameters for vias: drill diameter and annular ring thickness. Drill diameter is the diameter of the actual drilled hole in the PCB. The annular ring thickness is the thickness of the pad that surrounds the drilled hole. These dimensions are shown pictorially in Figure 5.

To determine the diameter of the finished via, use the following formula:

Finished via diameter = Drill diameter + 2 x (Annular ring thickness)

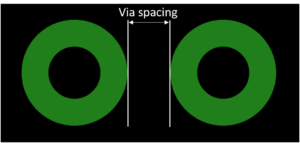

Via spacing is the distance between the edges of any two adjacent vias as shown in Figure 6. When placing vias, make sure the spacing between the vias match the trace spacing design rules that were chosen.

In this document, a “x/y via” indicates a via with drill diameter of x mils and finished via diameter of y mils. For example, a 12/24 via indicates a via with drill diameter of 12mils and finished via diameter of 24mils.

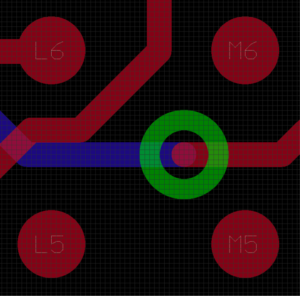

3.2.1 Example: A 12/24 via between 4 pads of the OSD32MP15x

One 12/24 via can be easily placed between four adjacent balls of the BGA as shown in Figure 7. A 12/24 via falls under Standard Manufacturing capabilities of most PCB manufacturers. It is relatively cheaper than much smaller vias.

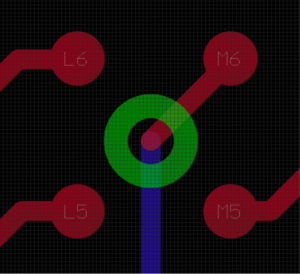

3.2.2 Example: A 10/18 via and 5/5 trace between 4 pads of the OSD32MP15x

Figure 8 shows one 10/18 via and one 5/5 trace between four adjacent pads of OSD32MP15x.

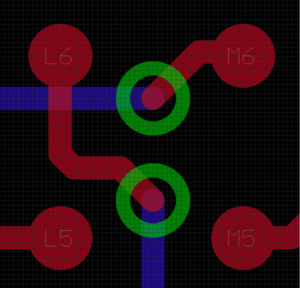

3.2.3 Example: Two 10/16 vias between 4 pads of the OSD32MP15x

In case of a tighter design, two 10/16 vias can be placed between four adjacent balls of the BGA as shown in Figure 9. A 10/16 via falls under Extended Manufacturing capabilities of most PCB manufacturers. This via size may be slightly more expensive than 12/24 via. However, based on your manufacturer’s capabilities and your design requirements, you could choose to use a much smaller via than 10/16.

4 OSD32MP15x Layout Examples

Once the design rules for traces and vias have been chosen for the PCB, the BGA can now be routed. The following sections provide examples of how to lay out the OSD32MP15x.

4.1 Signal Pin Fanout

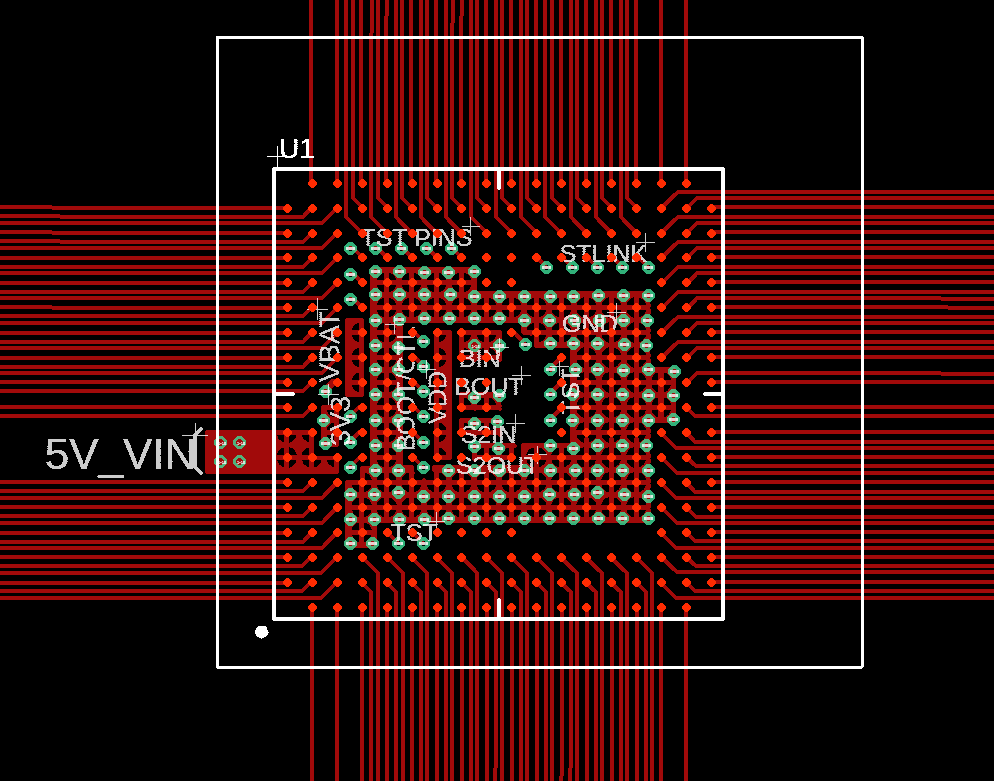

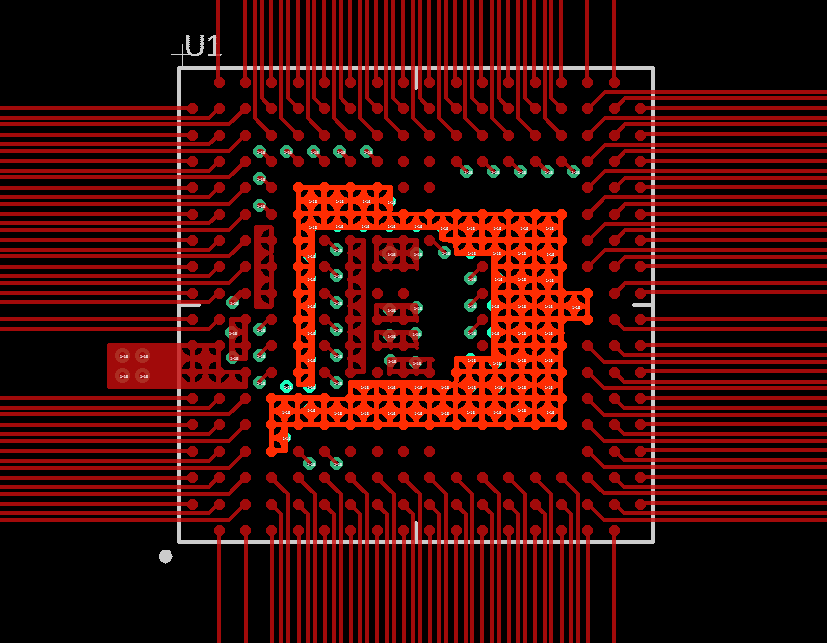

Figure 10 shows the fanout of all pads of the OSD32MP15x using 5/5 traces.

4.2 Power Inputs

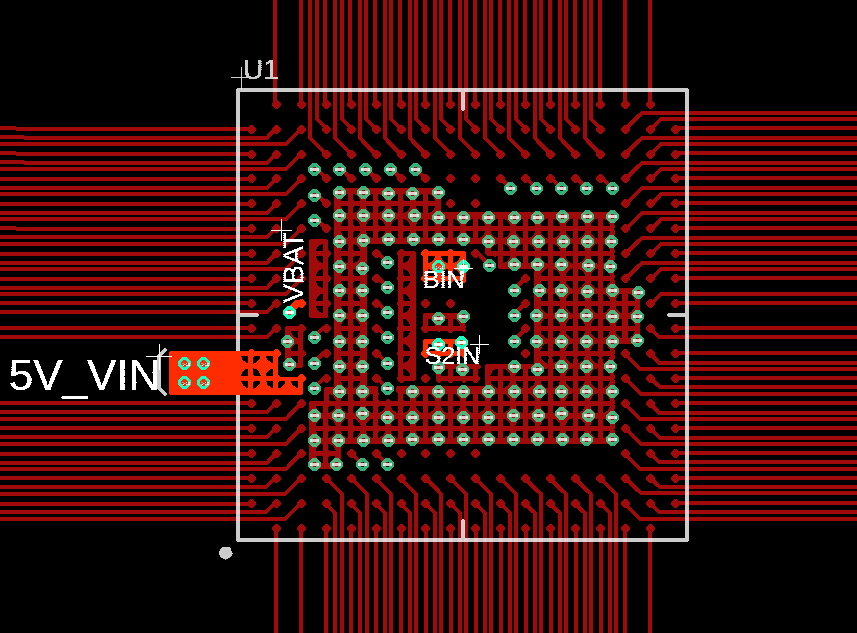

Power to the two input power rails (5V_VIN and VBAT) of the OSD32MP15x can be supplied through a copper pour and vias as shown in Figure 11 (Note: PMIC_LDO25IN is sourced by VIN in the below pictures representing typical use case).

4.3 Power Outputs

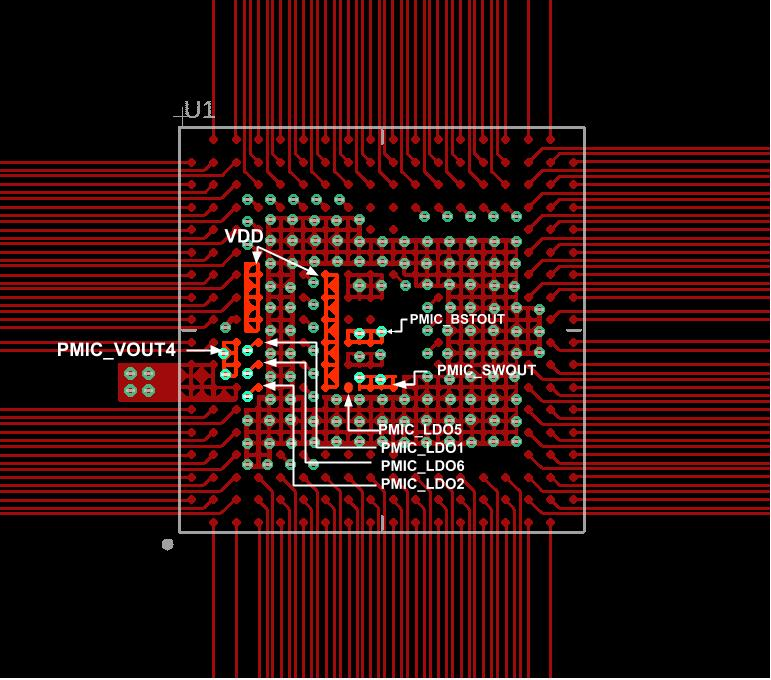

Power from the output power rails of the OSD32MP15x can be connected to the rest of the PCB using copper pours as shown in Figure 12.

4.4 Ground Connections

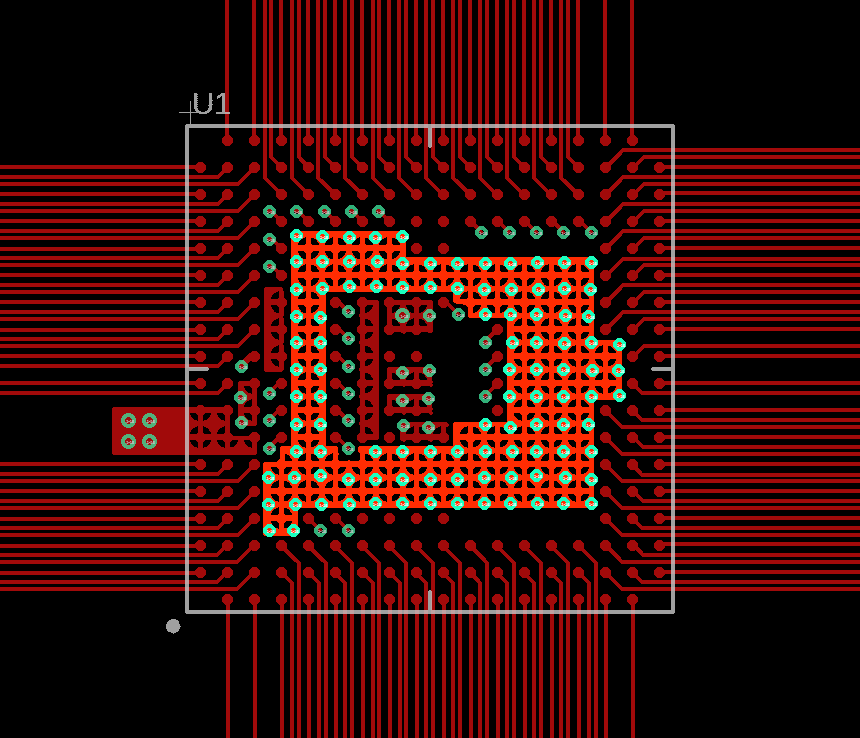

The ground pins of the OSD32MP15x can be connected to ground plane using copper pours as shown in Figure 13.

For space constrained design, the ground copper pours can also be configured as shown in Figure 14.

4.5 EEPROM

The write protect pin of the EEPROM (EEPROM_WP) of the OSD32MP15x needs to be driven low before information can be written into it. This can be done in many ways: The EEPROM_WP pin can be driven by another device on the PCB; It can be driven by one of the OSD32MP15x pins; It can be routed to a pad to be driven by an external device; It can be routed to a jumper; etc.

Figure 15 shows an example of the EEPROM_WP pin routed to a jumper using 100mil header. The other side of the jumper is connected to GND which allows the EEPROM_WP signal to be easily driven low. This can be a useful layout in prototype designs that are not space constrained.

5 References

6 Revision History

Get notified of updates to this Application Note and all of our Technical Documentation.

"*" indicates required fields

| Revision Number | Revision Date | Changes | Author |

|---|---|---|---|

| 1 | 02/18/2019 | Initial Release | Eshtaartha Basu |

| 2 | 03/18/2019 | Updated All Figures | Eshtaartha Basu |

| 3 | 08/06/2020 | Updated Ground Pour Recommendations | Justin Berry |